Sama seperti file kode yang berisi satu atau lebih baris kode sebagai konten agar bermanfaat, makefile dasar dibuat menggunakan variabel, aturan, dan target. Selain itu, ada faktor lain yang diperlukan untuk membuat makefile lengkap tanpa masalah. Dalam panduan ini, kita akan membahas sintaks dasar makefile dan masalah umum saat menulis makefile dan memberikan solusi untuk mengatasi masalah tersebut.

Memahami Sintaks Dasar Makefile

Untuk memulai pembuatan makefile, kami menjelaskan properti dasar makefile melalui contoh kode makefile. Penting untuk menyertakan properti sintaksis berikut dalam konten makefile untuk mendapatkan file yang dapat dieksekusi:

Variabel s: Data dasar yang menyimpan objek yang diperlukan untuk digunakan dalam makefile. Variabel-variabel ini digunakan untuk menentukan kompiler, flag, file sumber, file objek, dan file target. Dalam contoh makefile berikut, terdapat total lima variabel yaitu CXX (untuk menyetel kompiler C++), CXXFLAGSc (flag kompiler), TARGET (untuk menyetel nama file target yang dapat dieksekusi), SRCS (untuk menyetel file kode sumber) , OBJS (untuk memuat file objek yang dihasilkan melalui file kode sumber).

Target: Output yang diharapkan untuk dibangun dari sumbernya. Ini bisa berupa file target atau nama simbolis apa pun: 'semua' adalah target default yang harus dibuat melalui variabel 'TARGET', '$TARGET' bergantung pada variabel 'OBJS', dan target 'bersih' menghapus target dan file objek dari direktori kerja.

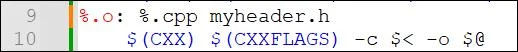

Aturan dan Perintah Pembuatan: Kumpulan instruksi dasar yang harus dijalankan untuk membuat target dari file sumber atau dependensi. Misalnya, aturan “%.o: %.cpp” menampilkan bahwa file dengan ekstensi “cpp” digunakan untuk membuat file objek dengan ekstensi “o” sementara kedua file berisi nama yang sama. Di sisi lain, perintah build $(CXX) $(CXXFLAGS) -o $(TARGET) $(OBJS) digunakan untuk menghubungkan file objek dan file target baru bersama-sama. Dengan cara yang sama, perintah build $(CXX) $(CXXFLAGS) -c $< -o $@ mengkompilasi file sumber menjadi file objek.

Ketergantungan: Dependensi selalu ada saat Anda ingin membuat makefile. Misalnya, target “semua” bergantung pada variabel “TARGET” sedangkan “TARGET” bergantung pada variabel “OBJS”. Pada saat yang sama, variabel “OBJS” bergantung pada file sumber melalui variabel “SRCS”.

Komentar: Instruksi yang dapat dimengerti manusia biasanya digunakan untuk menjelaskan tujuan baris kode jika Anda menggunakan file setelah waktu yang lama. Pada makefile berikut, kami menggunakan komentar yang dimulai dengan tanda “#” untuk menjelaskan setiap baris.

CXX = g++

CXXFLAGS = -std =c++ sebelas -Dinding

SASARAN = Baru

SRCS = main.cpp

OBJS = $ ( SRCS:.cpp=.o )

semua: $ ( TARGET )

$ ( TARGET ) : $ ( OBJS )

$ ( CXX ) $ ( BENDERA CXX ) -HAI $ ( TARGET ) $ ( OBJS )

% .HAI: % .cpp

$ ( CXX ) $ ( BENDERA CXX ) -C $ < -HAI $ @

membersihkan:

rm -F $ ( TARGET ) $ ( OBJS )

Masalah Umum dan Solusinya

Saat menulis makefile apa pun, penting untuk mempertimbangkan setiap detail kecil untuk mendapatkan hasil yang diinginkan di akhir. Beberapa masalah umum yang sering dihadapi oleh pengguna saat membuat makefile. Pada bagian ini, kami akan membahas masalah-masalah tersebut dan menyarankan kemungkinan solusi sebagai berikut:

1: Tidak Menggunakan Variabel

Menggunakan variabel dalam makefile adalah suatu keharusan karena diperlukan untuk mengatur kompiler, target, file sumber, dll. Masalah paling umum yang dapat ditemui adalah tidak menggunakan variabel apa pun dalam makefile. Oleh karena itu, pastikan untuk menggunakan variabel penting seperti CXX, CXXFLAGSc(compiler flags), TARGET, SRCS, dan OBJS pada contoh makefile sebelumnya.

2: Masalah Pemisah Hilang

Saat menulis makefile, penting untuk mempertimbangkan aturan indentasi dengan sangat hati-hati karena menggunakan spasi dan bukan tab akan membawa Anda ke masalah “pemisah yang hilang” selama pelaksanaan instruksi “make”. Misalnya, kita menambahkan spasi di awal aturan pada baris 13 dan menghapus tab.

$ ( TARGET ) : $ ( OBJS )$ ( CXX ) $ ( BENDERA CXX ) -HAI $ ( TARGET ) $ ( OBJS )

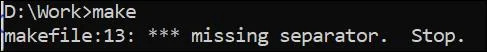

Setelah eksekusi kueri “make”, kami mendapatkan kesalahan “pemisah hilang” di baris 13, dan file berhenti berjalan. Untuk menghindari masalah ini, pastikan untuk menggunakan “tab” dan bukan spasi.

membuat

Untuk menghindari masalah ini, pastikan untuk menggunakan “tab” dan bukan spasi seperti yang digambarkan dalam gambar berikut:

$ ( TARGET ) : $ ( OBJS )$ ( CXX ) $ ( BENDERA CXX ) -HAI $ ( TARGET ) $ ( OBJS )

3: Masalah “Titik Masuk Tidak Ditemukan”.

Kesalahan ini sebagian besar terjadi karena file sumber dan bukan karena makefile seperti ketika Anda melewatkan penggunaan fungsi “main()” di file kode sumber. Misalnya, kita mengganti definisi fungsi main() dengan deklarasi fungsi sederhana yang ditentukan pengguna.

#termasukke dalam pertunjukan ( ) {

karakter v;

std::cout << 'Masukkan nilai:' ;

std::cin >> di dalam;

std::cout << di dalam << std::endl;

kembali 0 ;

}

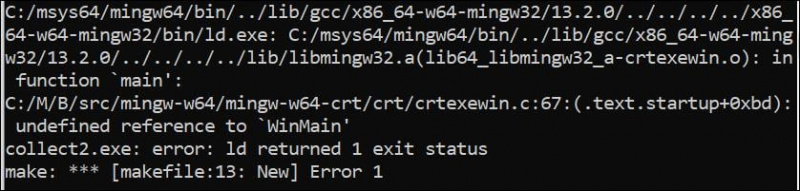

Saat menjalankan instruksi 'make' pada command prompt Windows, kami menemukan 'referensi tidak terdefinisi ke 'WinMain''. Ini karena kompiler tidak menemukan titik masuk untuk mulai mengeksekusi file C++. Untuk mengatasinya, ganti “show” dengan “main”.

4: Penggunaan Ekstensi yang Salah

Terkadang, pengguna mungkin secara tidak sengaja menggunakan ekstensi yang salah untuk file sumber untuk digunakan di makefile. Penggunaan ekstensi yang salah akan menyebabkan kesalahan run-time, yaitu tidak ada aturan untuk membuat target. Kami membuat makefile untuk membuat file yang dapat dieksekusi dan objek untuk file C++. Pada baris ketujuh, kami menyediakan file sumber dengan ekstensi “c”.

CXX := g++BENDERA CXX := -std =c++ sebelas -Dinding

TARGET = baru

SRCS = utama.c

OBJS = $ ( SRCS:.cpp=.o )

Semua: $ ( TARGET )

$ ( TARGET ) : $ ( OBJS )

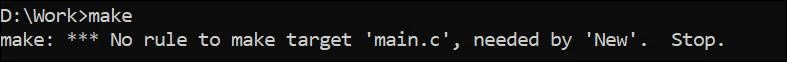

Menjalankan instruksi 'make' membawa kita ke kesalahan 'Tidak ada aturan untuk membuat target 'main.c''. Untuk menghindari masalah ini, pastikan untuk menggunakan ekstensi file sumber yang benar.

membuat

5: Ketergantungan Hilang

Saat menulis makefile, Anda harus menyertakan semua dependensi file sumber untuk mendapatkan hasil yang diinginkan. Misalnya, file kode C++ kami menggunakan file “myheader.h” sebagai ketergantungannya. Oleh karena itu, kami menyebutkannya dalam file kode C++ sebagai berikut:

#termasuk#sertakan “myheader.h”

ke dalam pertunjukan ( ) {

karakter v;

std::cout << 'Masukkan nilai:' ;

std::cin >> di dalam;

std::cout << di dalam << std::endl;

kembali 0 ;

}

Di dalam makefile, kami sengaja mengabaikan penggunaan file “myheader.h” dalam aturan build yang tertulis di baris 9.

% .HAI: % .cpp$ ( CXX ) $ ( BENDERA CXX ) -C $ < -HAI $ @

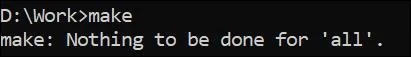

Sekarang, saat menggunakan instruksi “make”, kita menemukan kesalahan “Tidak ada yang harus dilakukan untuk 'semua'”.

membuat

$ ( CXX ) $ ( BENDERA CXX ) -C $ < -HAI $ @

Untuk menghindari masalah tersebut dan menjalankan kode sumber dengan sukses, sebutkan nama file “myheader.h” di baris kesembilan makefile seperti yang digambarkan berikut ini:

Kesimpulan

Dalam panduan ini, kami menjelaskan secara menyeluruh sintaks makefile menggunakan konten yang diperlukan seperti variabel, perintah build, aturan, dll. Contoh kode disertakan untuk menguraikan sintaksis dengan lebih jelas. Pada akhirnya, kita membahas beberapa masalah rutin dan solusinya yang mungkin ditemui pengguna saat membuat makefile.